# Lab 10: Analog to Digital Converter (ADC) Instructor: Prof. Yifeng Zhu Spring 2016

#### Goals

- 1. Understand basic ADC concepts, such as successive-approximation, sampling error, resolution, and data alignment

- 2. Map a GPIO pin to an ADC input

- 3. Use software trigger to make ADC conversions, and deploy polling method to read ADC results

- 4. Understand the tradeoff between conversion accuracy and conversion speed by configuring ADC sample time

- 5. Understand the concept of ADC resolution

- 6. Understand the difference between regular conversions and injected conversions for a sequence of ADC channels

#### **Pre-lab Assignment**

- 1. Read Chapter 20 Analog to Digital Conversion (ADC)

- 2. Complete the pre-lab assignment

#### Lab Demo

- 1. **Part 1**. When the voltage input is higher than 2.0V, the LED is light up. When the voltage is lower than 1.0V, the LED is off. The input voltage can be controlled manually by using a potentiometer. Use a voltage meter to verify it.

- 2. *Part 2*. Implement infrared (IR) proximity sensor. When an object gets close to the IR sensor, light up the LED.

- 3. *Something cool*. The following gives a few examples.

- a. Use a timer to periodically trigger the ADC

- b. Show the voltage measurement on the LCD (in terms of volts)

- c. Using the potentiometer to control the rotation speed of a stepper motor

- d. Count how many times your hand waves over the IR sensor

- e. Measure the distance of an object from the IR sensor

- f. Use the analog watchdog in the processor to trigger ADC when an object gets too close to the sensor

#### **Post-lab Assignment**

1. Write your answer in Readme.md and submit it to the gitlab server.

#### **Reference Voltage**

The reference voltage to the analog-to-digital (ADC) and digital- to-analog (DAC) converters can be provided externally or internally.

• If an *external* voltage is selected as the reference voltage, the external reference voltage should be applied to the VREF+ pin.

- If an *internal* voltage is selected as the reference voltage, the VREF+ pin can provide the reference voltage for external components.

- The internal voltage reference is enabled by setting the ENVR bit in the VREFBUF\_CSR register.

- The internal voltage reference can be selected by the VRS bits in the VREFBUF\_CSR register.

- If VRS is set, the voltage reference is ~2.5V.

- If VRS is cleared, the voltage reference is ~2.048V.

#### ADC: Migrating from STM32L1 to STM32L4

|                   | STM32L1                    | STM32L4                          |

|-------------------|----------------------------|----------------------------------|

| Instance          | ADC1                       | ADC1, ADC2, ADC3                 |

| May Decolution    | 12 bits                    | 12 bits, or                      |

| Max Resolution    | 12 Dits                    | 16 bits via digital oversampling |

| Mode              | single/continuous / scan / | single/continuous/scan/          |

| Mode              | discontinuous              | discontinuous dual mode          |

| Reference Voltage | External                   | External or internal             |

STM32L4 has a new ADC architecture. Register names and controls are different from STM32L1. Therefore, the flowchart given Figure 20-11 of Textbook (page 457) should be modified, as summarized below.

1. STM32L4 adds a new register named an *Analog Switch Control Register* (GPIO\_ASCR) for each GPIO port. When a bit in GIPO\_ASCR is set, the corresponding GPIO pin is connected to the ADC input. After setting the mode of PA.1 as analog, the following instruction is required to connect PA.1 to ADC.

where GPIO\_ASCR\_EN\_1 is defined in *stm32L476xx*. h as follows

#define GPIO\_ASCR\_EN\_1 ((uint32\_t)0x00000002)

#### 2. Steps to set up PA1 (ADC12\_IN6) for ADC1:

- 1. Enable ADC clock bit RCC AHB2ENR ADCEN in the RCC->AHB2ENR register.

- 2. Disable ADC1 by clearing the ADC\_CR\_ADEN in the ADC1->CR register.

- 3. Enable I/O analog switches voltage booster (SYSCFG\_CFGR1\_BOOSTEN) in the ADC123\_COMMON->CCR register.

- 4. Set ADC\_CCR\_VREFEN bit in the ADC123\_COMMON->CCR register to enable the conversion of internal channels. This is required to make conversion of internal channels.

- 5. Configure the ADC prescaler to select the frequency of the clock to the ADC (set clock not divided) in ADC123\_COMMON->CCR.

- 6. Configure ADC\_CCR\_CKMODE bits in ADC123\_COMMON->CCR to set the ADC clock mode as synchronous clock mode (HCLK/1).

- 7. Configure all ADCs as independent (clear ADC\_CCR\_DUAL bits) in ADC123\_COMMON>CCR

- 8. By default, the ADC is in deep-power-down mode where its supply is internally switched off to reduce the leakage currents. Therefore, software needs to wait up ADC. The ADC\_Wakeup() function is provided in the project template.

- 9. Configure RES bits in ADC1->CFGR to set the resolution as 12 bits.

- 10. Select right alignment in the ADC1->CFGR register.

- 11. Clear ADC\_SQR1\_L bits in ADC1->SQR1 to select 1 conversion in the regular channel conversion sequence.

- 12. Specify the channel number 6 as the 1st conversion in regular sequence (ADC1->SQR1)

- 13. Configure the channel 6 as single-ended (ADC1->DIFSEL).

- 14. Select ADC sample time in ADC1->SMPR1. The sampling time must be long enough for the input voltage source to charge the embedded capacitor to the input voltage level.

- 15. Select ADC as discontinuous mode by clearing the ADC\_CFGR\_CONT bits in ADC1->CFGR.

- 16. Clear ADC\_CFGR\_EXTEN bits in ADC1->CFGR to select software trigger

- 17. Enable ADC1 by setting the ADC\_CR\_ADEN bit in the ADC1->CR register

- 18. Wait until ADC1 is ready (i.e., wait until ADC\_ISR\_ADRDY bit in ADC1->ISR is set by hardware)

#### 3. Using the software to trigger one ADC conversion:

- 1. Software can start one ADC conversion by setting the ADC\_CR\_ADSTART bit in the ADC1->CR register

- 2. Software has to wait the completion of ADC conversion by checking whether ADC\_CSR\_EOC\_MST in the ADC123\_COMMON->CSR register has been set by the hardware.

- 3. The conversion result is saved in register ADC1->DR.

- **4. ADC Wakeup.** By default, the ADC is in deep-power-down mode where its supply is internally switched off to reduce the leakage currents.

```

void ADC Wakeup (void) {

int wait time;

// To start ADC operations, the following sequence should be applied

// DEEPPWD = 0: ADC not in deep-power down

// DEEPPWD = 1: ADC in deep-power-down (default reset state)

if ((ADC1->CR & ADC CR DEEPPWD) == ADC CR DEEPPWD)

ADC1->CR &= ~ADC CR DEEPPWD; // Exit deep power down mode if still in that state

// Enable the ADC internal voltage regulator

// Before performing any operation such as launching a calibration or enabling the ADC,

// the ADC voltage regulator must first be enabled and the software must wait for the

// regulator start-up time.

ADC1->CR |= ADC CR ADVREGEN;

// Wait for ADC voltage regulator start-up time

// The software must wait for the startup time of the ADC voltage regulator

// (T ADCVREG STUP, i.e. 20 us) before launching a calibration or enabling the ADC.

wait time = 20 * (80000000 / 1000000);

while(wait time != 0) {

wait_time--;

}

```

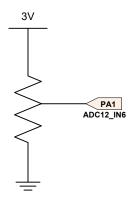

#### Part 1. Measuring the Input Voltage Adjusted by a Potentiometer

A potentiometer (pot) is a three-terminal variable resistor. It uses a sliding contact and works as an adjustable voltage divider. When two outer terminals connected to Vcc and the ground respectively, the center terminal generates a voltage that varies from 0 to Vcc, depending on the position of the sliding contact.

Figure 1. Measure the voltage from a potentiometer-based divider (Vcc = 3V)

The following refers to question 1 of the post-lab assignment. The objective is to identify the reference voltage.

• Use a multi-meter to measure the voltage on PA1:

Voltage of PA1 = \_\_\_\_\_

• In the debug environment, find out the value of the data register (DR) of the ADC:

ADC DR register = \_\_\_\_\_

• Calculate the reference voltage:

Reference voltage = \_\_\_\_\_

#### Part 2. Infrared (IR) Proximity Sensor

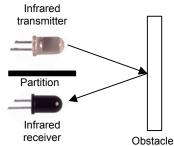

In this part, you will implement a very simple proximity sensor by using an infrared transmitter and an infrared receiver. When an obstacle moves closer, the infrared captures more infrared that is bounced back by the obstacle.

It is recommended to put a dark tape around the receiver or place a partition between the transmitter and receiver to reduce infrared leakage.

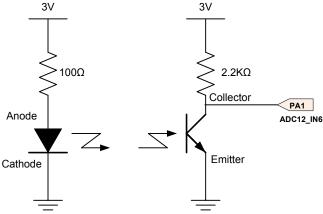

Figure 2. Infrared Proximity Sensor

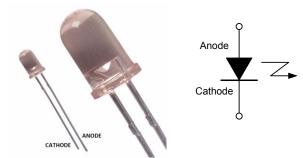

Figure 3. QED123 Infrared Light Emitting Diode (Infrared Transmitter)

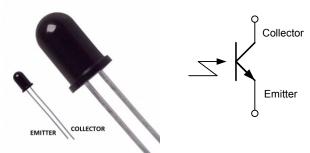

Figure 4. QSD124 Infrared Phototransistor (Infrared Receiver)

**Figure 5. Basic Connection Diagram**

### ECE 271 pre-Lab Assignment Lab 10: Analog to Digital Converter (ADC)

| <b>Student Name:</b> |  |

|----------------------|--|

| staucht Hame.        |  |

## 1. Setting of ADC Control Registers

|              | Decister        |       |             |         |             |       |           |             |         |           | <u> </u>                     | _    |                                                | 6            | <u></u>    | _    | 10           | 10                             | -        | ~             | <u> </u> |            |              | 1             | ı -             | 1            | 1           | 1        | 1            | Ι            |         |             |         |

|--------------|-----------------|-------|-------------|---------|-------------|-------|-----------|-------------|---------|-----------|------------------------------|------|------------------------------------------------|--------------|------------|------|--------------|--------------------------------|----------|---------------|----------|------------|--------------|---------------|-----------------|--------------|-------------|----------|--------------|--------------|---------|-------------|---------|

| Offset       | Register        | က်    | 3           | 56      | 28          | 2     | 26        | 5           | 5       | 23        | 2                            | 'n   | 7                                              | 13           | 18         | 7    | 16           | 15                             | 14       | 13            | 1,       | 11         | - 10         | ၈             | ω               | ^            | ဖ           | Ŋ        | 4            | က            | 7       | 7           | 0       |

| 0x00         | ADCx_ISR        | Res.  | Res.        | Res.    | Res.        | Res.  | Res.      | Res.        | Res.    | Res.      | Res.                         | Res. | Res.                                           | Res.         | Res.       | Res. | Res.         | Res.                           | Res.     | Res.          | Res.     | Res.       | JQOVF        | AWD3          | AWD2            | AWD1         | JEOS        | JEOC     | OVR          | EOS          | EOC     | EOSMP       | ADRDY   |

|              | Value           | +     |             |         |             |       |           |             |         |           |                              |      |                                                |              |            |      |              |                                |          |               |          |            | Ш            |               |                 |              |             |          |              |              | Н       | Е           | Е       |

| 0x04         | ADCx_IER        | Res.  | Res.        | Res.    | Res.        | Res.  | Res.      | Res.        | Res.    | Res.      | Res.                         | Res. | Res.                                           | Res.         | Res.       | Res. | Res.         | Res.                           | Res.     | Res.          | Res.     | Res.       | JQOVFIE      | <b>AWD3IE</b> | AWD2IE          | AWD1IE       | JEOSIE      | JEOCIE   | OVRIE        | EOSIE        | EOCIE   | EOSMPIE     | ADRDYIE |

|              | Value           |       |             |         |             |       |           |             |         |           |                              |      |                                                |              |            |      |              |                                |          |               |          |            |              |               |                 |              |             |          |              |              |         |             |         |

| 0x08         | ADCx_CR         | ADCAL | ADCALDIF    | DEEPPWD | ADVREGEN    | Res.  | Res.      | Res.        | Res.    | Res.      | Res.                         | Res. | Res.                                           | Res.         | Res.       | Res. | Res.         | Res.                           | Res.     | Res.          | Res.     | Res.       | Res.         | Res.          | Res.            | Res.         | Res.        | JADSTP   | ADSTP        | JADSTART     | ADSTART | SIGGY       | ADEN    |

|              | Value           |       |             |         |             |       |           |             |         |           |                              |      |                                                |              |            |      |              |                                |          |               |          |            |              |               |                 |              |             |          |              |              |         |             |         |

| 0x0C         | ADCx_CFGR       | Jadis | А           | .WD     | 1CF         | 1[4:0 | )]        | JAUTO       | JAWD1EN | AWD1EN    | AWD1SGL                      | JQM  | NUNSCION E E E E E E E E E E E E E E E E E E E |              |            |      | DISCEN       | Res. AUTDLY CONT               |          |               | OVRMOD   | EXTEN[1:0] |              |               | EXTSEL<br>[3:0] |              |             | ALIGN    | RE<br>[1:    | ES<br>:0]    | Res.    | DMACFG      | DMAEN   |

|              | Value           | -     |             |         |             |       |           |             |         |           |                              |      |                                                |              |            |      |              |                                |          |               |          |            |              |               |                 |              |             |          |              |              |         |             |         |

| 0x0C         | ADCx_CFGR2      | Res.  | Res.        | Res.    | Res.        | Res.  | Res.      | Res.        | Res.    | Res.      | Res.                         | Res. | Res.                                           | Res.         | Res.       | Res. | Res.         | Res.                           | Res.     | Res.          | Res.     | Res.       | ROVSM        | TROVS         | 0               | VSS          | S[3:0       | )]       |              | VSI<br>[2:0] |         | JOVSE       | ROVSE   |

|              | Value           |       |             |         | NAD         |       |           | NAD         |         |           | NAD:                         |      |                                                | MADA         | <u></u>    |      | NAD          |                                |          | MP            |          |            | MD           |               |                 | NAD:         |             |          | NAD.         |              | Щ       | MD          | Щ       |

| 0x14         | ADCx_SMPR1      | Res   | Res         |         | MP<br>[2:0] |       |           | MP<br>[2:0] |         |           | MP <sup>7</sup><br>[2:0]     |      |                                                | MP(<br>[2:0] |            |      | MP:<br>[2:0] |                                | _        | 101P<br>[2:0] |          |            | MP:<br>2:0]  |               |                 | MP:<br>[2:0] |             |          | MP [2:0]     |              |         | MP(<br>2:0] | ,       |

|              | Value           |       |             |         |             |       |           |             |         |           |                              |      |                                                |              |            |      |              |                                |          |               |          |            |              |               |                 |              |             |          |              |              |         |             |         |

| 0x18         | ADCx_SMPR2      | Ses.  | SMP18 (2:0] |         |             |       |           |             |         |           | SMP17 SMP16 SMP1 [2:0] [2:0] |      |                                                |              |            |      |              |                                |          | MP1<br>[2:0]  |          |            | MP1<br>[2:0] |               |                 | MP1<br>[2:0] |             |          | MP1<br>[2:0] |              |         | ИР1<br>2:0] | 0       |

| 0.00         | Value           |       | -           |         |             |       |           | [2.0]       | 1       |           |                              |      |                                                | [2.0]        | 1          |      | [2.0]        |                                |          | [2.0]         | l .      |            | 2.0]         |               | <u>'</u>        | [2.0]        |             | <u> </u> | [2.0]        | l            | H       | 2.0]        |         |

| 0x1C         | Reserved        |       | Res.        |         |             |       |           |             |         |           |                              |      |                                                |              |            |      |              |                                |          |               |          |            |              |               |                 |              |             |          |              |              |         |             |         |

| 0x20         | ADCx_TR1        | Res.  | Res.        | Res.    | Res.        |       | HT1[11:0] |             |         |           |                              |      |                                                |              |            |      |              |                                | Res.     | Res.          | Res.     |            |              |               |                 |              | LT1[        | 11:0     | )]           |              |         |             |         |

|              | Value           | 02    | (2)         | 00      | (2)         | (7)   | 10 0 0    |             |         |           |                              |      |                                                |              |            |      |              | (/)                            | 92       | <u>(?</u>     | (2)      | (2)        | (/)          | (2)           | <u>()</u>       |              |             |          |              |              |         |             |         |

| 0x24         | ADCx_TR2        | 2     | Ŷ           | Xe      | Ke          | Xe    | Ke        | Xe          | Xe      | -         | 1                            |      | HT2                                            | [[7:0        | )]         | 1    | ı            | P P P P P P P P P P P LT2[7:0] |          |               |          |            |              |               |                 |              |             |          |              |              |         |             |         |

|              | Value ADCx_TR3  | S)    | 00          | S       | S)          | S)    | O)        | S)          | S       |           | <u> </u>                     | L    | L                                              |              |            |      | <u> </u>     | S                              | S        | S             | S        | S          | S            | S             | es<br>S         |              |             |          |              | [7.0         | Ш,      |             |         |

| 0x28         | Value           | Y     | Y           | Y       | Y           | Y     | Y         | Y           | Y       |           | ı                            | Ι    | HI3                                            | [[7:0        | ) <u>]</u> |      | I            | Y                              | Y        | Y             | Y        | Y          | ĸ            | ĸ             | ĸ               |              |             |          | LT3          | [7:0         |         | 0           | 0       |

| 0x2C         | Reserved        | t     | 1           |         |             |       |           |             |         | 1         | l                            |      | l                                              | l            |            |      | R            | es.                            |          |               | l        |            |              |               | l               |              |             |          |              | l            |         |             | Ü       |

| 0x30         | ADCx_SQR1       | Res.  | Res.        | Res.    |             | SC    | )4[4:     | :0]         |         | Res.      |                              | SQ   | 3[4:                                           | 0]           |            | Res. |              | SC                             | 2[4:     | 0]            |          | Res.       |              | SQ            | 1[4:            | 0]           |             | Res.     | Res.         |              | L[3:    | :0]         |         |

|              | Value           |       |             |         |             |       |           |             |         |           |                              |      |                                                |              |            |      |              |                                |          |               |          |            |              |               |                 |              |             |          |              |              |         |             |         |

| 0x34         | ADCx_SQR2       | Res.  | Res.        | Res.    |             | SC    | 9[4:      | :0]         |         | Res.      |                              | SQ   | 8[4:                                           | 0]           |            | Res. |              | SC                             | 7[4:     | 0]            |          | Res.       |              | SQ            | 6[4:            | 0]           |             | Res.     |              | SC           | )5[4:   | 0]          |         |

| 0,10         | Value           |       |             |         |             |       |           |             |         |           |                              |      |                                                |              |            |      |              |                                |          |               |          |            |              |               |                 |              |             |          |              |              |         |             |         |

|              | ADCx_SQR3       | Res.  | ses.        | Res.    |             | SQ    | 14[4      | :0]         |         | Ses.      |                              | SQ   | 13[4                                           | :0]          |            | Res. |              | SQ                             | 12[4     | :0]           |          | Res.       |              | SQ            | 11[4            | :0]          |             | Res.     |              | SQ           | 10[4    | :0]         |         |

| 0x38         | Value           |       | Ľ           |         | L           |       | Ľ         | Ĺ           |         |           |                              | L    | Ĺ                                              | Ĺ            | L          |      | t            |                                | Ĺ        | Ė             | L        | CC         |              | L             | Ė               | Ė            | L           |          | L            | L            |         |             |         |

| 0x3C         | ADCx_SQR4       | Res.  | Res.        | Res.    | Res.        | Res.  | Res.      | Res.        | Res.    | Res.      | Res.                         | Res. | Res.                                           | Res.         | Res.       | Res. | Res.         | Res.                           | Res.     | Res.          | Res.     | Res.       |              | SQ            | 16[4            | :0]          |             | Res.     |              | SQ           | 15[4    | :0]         |         |

| 0,00         | Value           |       | Ľ           |         |             |       | ľ         |             |         |           |                              |      |                                                |              | Ľ          |      |              |                                |          |               |          | -          | E            |               | Ė               | Ė            |             |          |              |              |         |             |         |

| 0x40         | ADCx_DR         | Res.  | Res.        |         |             |       |           |             |         |           |                              |      |                                                |              |            | Res. |              |                                |          |               | -        | regu       | ılar F       | RDA           | TA[1            | 15:0]        |             |          |              |              |         |             |         |

| UA-10        | Value           |       |             |         |             |       |           |             |         |           |                              |      |                                                |              |            |      |              | E                              | L        |               |          |            | Ē            |               |                 | Ĺ            |             |          |              |              |         |             |         |

| 0x44-        | Reserved        | Res.  |             |         |             |       |           |             |         |           |                              |      |                                                |              |            |      |              |                                |          |               |          |            |              |               |                 |              |             |          |              |              |         |             |         |

| 0x48<br>0x4C | ADCx_JSQR Value | Res.  |             | JS      | Q4[4        | i:0]  |           | Res.        |         | JSQ3[4:0] |                              |      |                                                |              |            |      |              | :0]                            |          | Res.          |          | JSC        | Q1[4         | :0]           |                 |              | JEXTEN[1:0] | J        | EXT<br>[3:   |              | -       | JL[ŕ        | 1:0]    |

|              | . 3100          |       | 1           | 1       | 1           | 1     | <u> </u>  | 1           | 1       | 1         | <u> </u>                     | 1    |                                                |              | <u> </u>   | 1    | <u> </u>     |                                | <u> </u> | 1             |          |            |              | 1             | <u> </u>        | 1            | i i         | 1        | 1            |              |         |             | . !     |

| Offset        | Register           | 31         | 30       | 29        | 28           | 27        | 56    | 25   | 24   | 23   | 22       | 21   | 20                                    | 19           | 18       | 17   | 16   | 15   | 14       | 13       | 12       | <del>-</del> 5 | 2           | 6    | <b>&amp;</b>  |      | 9    | 2     | 4    | ဗ        | 7    | 1             | 0    |

|---------------|--------------------|------------|----------|-----------|--------------|-----------|-------|------|------|------|----------|------|---------------------------------------|--------------|----------|------|------|------|----------|----------|----------|----------------|-------------|------|---------------|------|------|-------|------|----------|------|---------------|------|

| 0x50-<br>0x5C | Reserved           |            |          |           |              |           |       |      |      |      |          |      |                                       |              |          |      |      | es.  |          |          |          |                |             |      |               |      |      |       |      |          |      |               |      |

| 0x60          | ADCx_OFR1          | OFFSET1_EN |          | OFF<br>Cł | SET<br>H[4:0 | Γ1_<br>)] |       | Res. | Res. | Res. | Res.     | Res. | Res.                                  |              |          | Res. | Res. | Res. | Res.     | Res.     | Res.     |                |             |      | OFFSET1[11:0] |      |      |       |      |          |      |               |      |

|               | Value              |            |          |           |              |           |       |      |      |      |          |      |                                       |              |          |      |      |      |          |          |          |                |             |      |               |      |      |       |      |          |      |               |      |

| 0x64          | ADCx_OFR2          | OFFSET2_EN |          | OFF<br>Ch | SET<br>H[4:0 | Γ2_<br>)] |       | Res. | Res. | Res. | Res.     | Res. | % % % % % % % % % % % % % % % % % % % |              |          |      |      |      |          |          |          | )FFS           | FSET2[11:0] |      |               |      |      |       |      |          |      |               |      |

|               | Value              |            |          |           |              |           |       |      |      |      |          |      |                                       |              |          |      |      |      |          |          |          |                |             |      |               |      |      |       |      |          |      |               |      |

| 0x68          | ADCx_OFR3          | OFFSET3_EN |          | OFF<br>CH | SET<br>H[4:0 |           |       | Res. | Res. | Res. | Res.     | Res. | Res.                                  | Res.         | Res.     | Res. | Res. | Res. | Res.     | Res.     | Res.     |                |             |      | 0             | FFS  | SET3 | 3[11: | 0]   |          |      |               |      |

|               | Value              |            |          |           |              |           |       |      |      |      |          |      |                                       |              |          |      |      |      |          |          |          |                |             |      |               |      |      |       |      |          |      |               |      |

| 0x6C          | ADCx_OFR4          | OFFSET4_EN |          | OFF<br>Ch | SET<br>H[4:0 | Γ4_<br>)] |       | Res. | Res. | Res. | Res.     | Res. | Res.                                  | Res.         | Res.     | Res. | Res. | Res. | Res.     | Res.     | Res.     |                |             |      |               |      |      |       |      |          |      |               |      |

|               | Value              |            |          |           |              |           |       |      |      |      |          |      |                                       |              |          |      |      |      |          |          |          |                |             |      |               |      |      |       |      |          |      |               |      |

| 0x70-<br>0x7C | Reserved           |            |          |           |              | ı         | 1     | 1    |      | ı    |          |      |                                       |              |          | 1    | Res. |      |          |          |          |                |             |      |               |      |      |       |      |          |      |               |      |

| 0x80          | ADCx_JDR1          | Res.       | Res.     | Res.      | Res.         | Res.      | Res.  | Res. | Res. | Res. | Res.     | Res. | Res.                                  | Res.         | Res.     | Res. | Res. |      |          |          |          |                |             | JDA  | ATA           | 1[15 | 5:0] |       |      |          |      |               |      |

| 0,00          | Value              |            |          |           |              |           |       |      |      |      |          |      |                                       |              |          |      |      |      |          |          |          |                |             |      |               |      |      |       |      |          |      |               |      |

| 0x84          | ADCx_JDR2  Value   | Res.       | Res.     | Res.      | Res.         | Res.      | Res.  | Res. | Res. | Res. | Res.     | Res. | Res.                                  | Res.         | Res.     | Res. | Res. |      |          | ı        |          |                |             | JDA  | ATA:          | 2[15 | 5:0] |       |      |          |      |               |      |

|               | ADCx_JDR3          | Š.         | Š.       | S.        | S.           | Š         | S.    | S.   | S.   | Š.   | S.       | S.   | S.                                    | S            | Š.       | S.   | S.   |      |          | <u> </u> |          |                |             |      |               | 0545 |      |       |      | <u> </u> | ш    |               |      |

| 0x88          | Value              | Re         | Re       | R         | Re           | Re        | Re    | Re   | Re   | Re   | Re       | Re   | Re                                    | Re           | Re       | Re   | Re   |      | I        | ı        | I        |                | -           | JDA  | AIA           | 3[15 | o:0] |       |      | l        |      |               | _    |

|               | ADCx_JDR4          | 30         | Š        | S.        | 9            | S.        | Ś     | ŝ    | 9    | SS.  | Š        | SS.  |                                       | 9            | Ś        | 9    | S.   |      | <u> </u> | <u> </u> | <u> </u> |                |             | 10   |               | 4545 | . 01 |       |      | <u> </u> |      |               | -    |

| 0x8C          | Value              | ď          | Ř        | Ř         | Ř            | ×         | X     | Ř    | Ř    | ×    | Ř        | Ř    | Ř                                     | Ř            | ×        | Ř    | Ř    |      | I        | T .      | I        |                | 1           | JDA  | AIA           | 4[15 | 0:0] |       |      | ı        | П    | $\overline{}$ | _    |

| 0x8C-<br>0x9C | Reserved           |            | <u> </u> | ı         |              | l         | ı     | ı    |      | l    | <u> </u> |      |                                       |              |          | I    | R    | es.  |          | ı        |          | <u> </u>       |             |      |               |      |      |       |      | l        |      |               |      |

| 0xA0          | ADCx_AWD2CR        | Res.       | Res.     | Res.      | Res.         | Res.      | Res.  | Res. | Res. | Res. | Res.     | Res. | Res.                                  | Res.         |          |      |      |      |          |          |          | ΑW             | /D2         | CH[  | 18:0          | 0]   |      |       |      |          |      |               |      |

| UXAU          | Value              | 11.        |          | 1         |              |           |       |      |      |      |          |      |                                       |              |          |      |      |      |          |          |          |                |             |      |               |      |      |       |      |          |      |               |      |

| 0xA4          | ADCx_AWD3CR        | Res.       | Res.     | Res.      | Res.         | Res.      | Res.  | Res. | Res. | Res. | Res.     | Res. | Res.                                  | Res.         |          |      |      |      |          |          |          | ΑW             | /D3         | CH[  | 18:0          | 0]   |      |       |      |          |      |               |      |

| 024           | Value              |            |          |           | -            |           | laba. |      | -    |      |          |      |                                       |              |          |      |      |      |          |          |          |                |             |      |               |      |      |       |      |          |      |               |      |

| 0xA8-<br>0xAC | Reserved           | Res.       | Res.     | Res.      | Res.         | Res.      | Res.  | Res. | Res. | Res. | Res.     | Res. | Res.                                  | Res.         | Res.     | Res. | Res. | Res. | Res.     | Res.     | Res.     | Res.           | Yes.        | Res. | Res.          | Res. | Res. | Res.  | Res. | Res.     | Res. | Res.          | Res. |

| 0xB0          | ADCx_DIFSEL        | Res.       | Res.     | Res.      | Res.         | Res.      | Res.  | Res. | Res. | Res. | Res.     | Res. | Res.                                  | DIFSEL[18:0] |          |      |      |      |          |          |          |                |             |      |               |      |      |       |      |          |      |               |      |

| 004           | Value ADCx_CALFACT | Res.       | Res.     | Res.      | Res.         | Res.      | Res.  | Res. | Res. | Res. |          | CA   | LFA                                   | CT_          | T_D[6:0] |      |      |      |          |          |          |                |             |      |               |      | 0]   |       |      |          |      |               |      |

| 0xB4          | Value              | Ì          |          |           |              |           |       |      |      |      |          |      |                                       |              |          |      |      |      |          |          |          |                |             |      |               |      |      |       |      |          |      |               |      |

# 2. Master and slave ADC common registers (ADC123\_COMMON)

| Offset | Register | 31   | 30              | 29   | 28   | 27   | 26        | 25       | 24       | 23      | 22     | 21         | 20      | 19  | 18      | 17          | 16        | 15        | 14   | 13     | 12   | 7    | 10        | တ        | ∞        | 7        | 9        | 2    | 4       | 3    | 7    | _         | 0         |

|--------|----------|------|-----------------|------|------|------|-----------|----------|----------|---------|--------|------------|---------|-----|---------|-------------|-----------|-----------|------|--------|------|------|-----------|----------|----------|----------|----------|------|---------|------|------|-----------|-----------|

| 0x00   | ADCx_CSR | Res. | Res.            | Res. | Res. | Res. | JQOVF_SLV | AWD3_SLV | AWD2_SLV | AWD1_   |        | A JEOC_SLV | OVR_SLV | EOS | EOC_SLV | EOSMP_SLV   | ADRDY_SLV | Res.      | Res. | Res.   | Res. | Res. | JQOVF_MST | AWD3_MST | AWD2_MST | AWD1_MST | JEOS_MST | JEOC | OVR_MST | EOS_ |      | EOSMP_MST | ADRDY_MST |

|        | Value    |      |                 |      |      |      |           |          |          |         |        |            |         |     |         |             |           |           |      |        |      |      |           |          |          |          |          |      |         |      |      |           |           |

| 0x04   | Reserved |      | Res.            |      |      |      |           |          |          |         |        |            |         |     |         |             |           |           |      |        |      |      |           |          |          |          |          |      |         |      |      |           |           |

| 0x08   | ADCx_CCR | Res. | Res.            | Res. | Res. | Res. | Res.      | Res.     | CH18SEL  | CH17SEL | VREFEN | PF         | RES     | C[3 | :0]     | CKMODE11-01 |           | MDMA[1·0] |      | DMACFG | Res. | DI   | ELA       | Y[3:     | :0]      | Res.     | Res.     | Res. |         | DU   | AL[4 | 1:0]      |           |

|        | Value    |      |                 |      |      |      |           |          |          |         |        |            |         |     |         |             |           |           |      |        |      |      |           |          |          |          |          |      |         |      |      |           |           |

|        | ADCx_CDR |      | RDATA_SLV[15:0] |      |      |      |           |          |          |         |        |            |         |     |         |             |           |           |      |        | R    | DAT  | L_A       | MST      | [15      | 0]       |          |      |         |      |      |           |           |

| 0x0C   | Value    |      |                 |      |      |      |           |          |          |         |        |            |         |     |         |             |           |           |      |        |      |      |           |          |          |          |          |      |         |      |      |           |           |

# ECE 271 Lab Demo Lab 10: Analog to Digital Converter (ADC)

Demo Part 1, Part 2, and something cool to TA.

#### ECE 271 post-Lab Assignment Lab 10: Analog to Digital Converter (ADC)

Write your answer to the following questions in Readme.md and submit it to the gitlab server.

1. For 12-bit ADC, we know that

ADC Result =

$$floor\left(2^{12} \times \frac{V}{V_{REF}} + \frac{1}{2}\right)$$

Design an experiment to find out  $V_{REF}$

- 2. When the voltage output from the potentiometer-based voltage divider is lower than 1.0V, the LED is turned off. What constant value should the ADC DR register be compared with?

- 3. When the voltage output from the potentiometer-based voltage divider is higher than 2.0V, the LED is light up. What constant value should the ADC DR register be compared with?

- 4. What is the maximum distance at which your sensor can reliably detect your hand?